etc/systemd/network/dev Įnsure rvice is started/enabled afterwards. Create the following file (where hostname is your machine's hostname): This may be desirable for systems without a wired Ethernet adapter. Thus, the expected eth0 name must be retained by following Network configuration#Revert to traditional interface names.Īlternatively, a dummy eth0 network interface can be dynamically created by systemd-networkd at boot. However, network interfaces use predictable names by default-these can vary from machine to machine.

#Modelsim altera path v90 license#

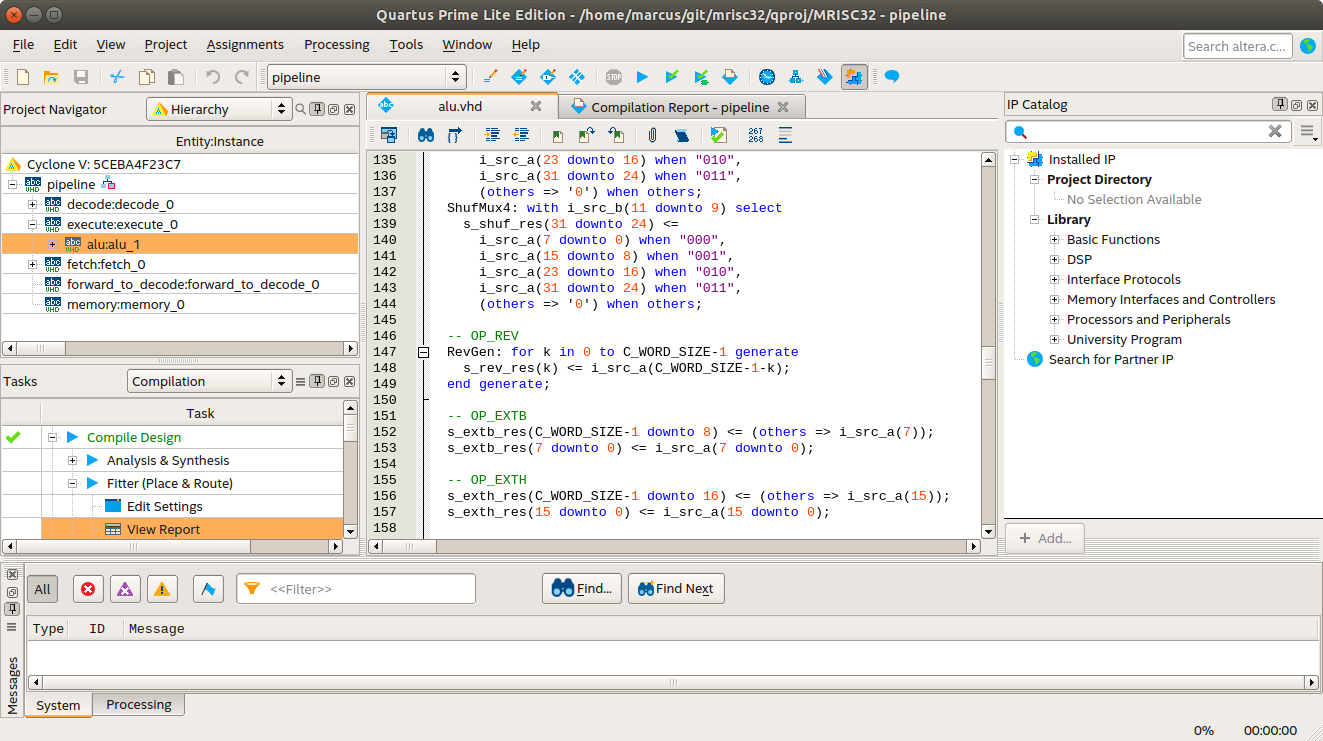

The license validation routine looks for your MAC address on interface eth0, the traditional name for your Ethernet controller. See vsim -help for more information.Ĭonfiguring the path to your Quartus Prime Standard Edition license file from the Quartus Prime settings interface is not enough for successful license validation. Run ModelSim by running vsim or selecting its desktop entry. See quartus_sh -help for more information. Use the quartus_sh utility to run Quartus Prime Shell.

Run Quartus Prime Lite by running quartus or selecting its desktop entry. Quartus-free-quartus uses files in /etc/profile.d/ to extend the PATH environment variable, so log into a new session to make commands like quartus_sh available.īeing in the plugdev group to program an FPGA (via the USB-Blaster) is optional logged in users are always allowed access.

#Modelsim altera path v90 install#

Those who do not wish to do so can install the last version of ModelSim ( modelsim-intel-starter AUR) instead. However, obtaining a valid license file is required for Questa. See also quartus-130 AUR for the SP1 Subscription Edition.Īs mentioned, Questa replaces ModelSim. Quartus II 13.0 Web Edition is "the last version to support Cyclone II and earlier FPGAs", so install quartus-free-130 AUR instead of quartus-free if support for such devices is needed. For example, install the quartus-free-devinfo-cyclonev AUR dependency if you have a Cyclone V FPGA. Quartus-free-quartus requires quartus-free-devinfo, which is provided by any one of the packages with a quartus-free-devinfo- prefix.

Quartus Prime Lite and Questa can be installed with the quartus-free AUR meta-package. (Discuss in Talk:Intel Quartus Prime#Minimal installation)

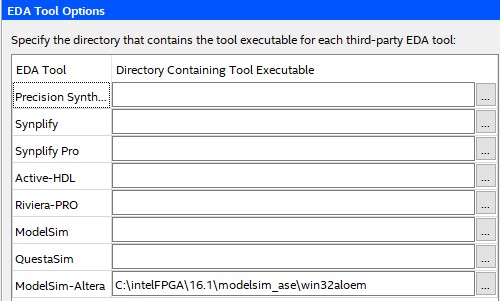

The process of building some components is very resource-intensive, so saying "minimal installation" here is misleading. Since quartus-free AUR is a split package, installing even a single dependency will result in all other components being built as well. I went to EDAtool setting and selected ModelSim-altera and Verilog_HDL and set simulation setting to simulation/modelsimĪfter adjusting the simulation setting to 'simulation/modelsim-altera' instead of just 'modelsim' my flow simulations compiled properly.Reason: makepkg(8) does not support building split packages in a PKGBUILD. I adjusted the Modelsim-altera pathway to C:\intelFPGA_lite\18.1\modelsim_ase\win32aloem in settings. 1 >error, 1 warningĮrror: Peak virtual memory: 4647 megabytesĮrror: Processing ended: Fri Dec 06 04:12:54 2019Įrror: Total CPU time (on all processors): 00:00:01 Testbench_vector_input_file option does not existĮrror: Quartus Prime EDA Netlist Writer was unsuccessful. Luckily however I figured it out and am making this post with the intention of hopefully saving someone who encounters this same issue some time.Įrror (199014): Vector source file >C:/intelFPGA_lite/18.1/Waveform.vwf specified with. Tonight I encountered this issue and it took me close to half hour to trouble shoot. How do you fix a non-existent directory path in Quartus II?

0 kommentar(er)

0 kommentar(er)